4️⃣ 프로세서 구조와 동작 원리

컴퓨터의 프로세서(Processor) 는 데이터를 가져오고, 연산을 수행하고, 저장하는 일련의 과정을 거칩니다.

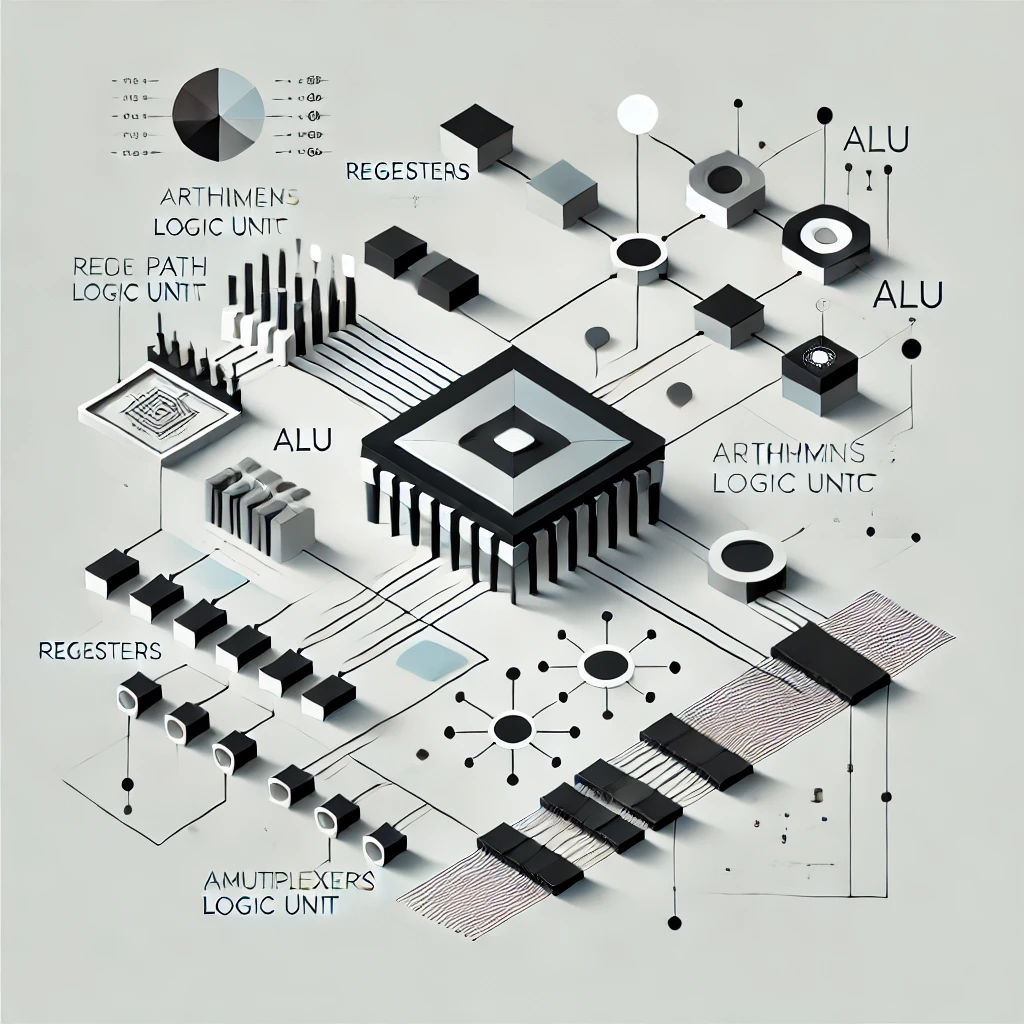

이러한 과정에서 데이터가 흐르는 경로를 데이터패스(Data Path) 라고 합니다.

데이터패스는 CPU 내부에서 명령어 실행을 위한 데이터의 이동 경로를 정의하며,

연산 장치(ALU), 레지스터, 멀티플렉서, 버스, 제어 신호 등의 요소로 구성됩니다.

이번 섹션에서는 데이터패스의 개념, 주요 구성 요소, 동작 원리, 그리고 현대 CPU에서의 데이터패스 최적화 기법을 자세히 살펴보겠습니다.

🔹 1. 데이터패스(Data Path)란?

✅ 1.1 데이터패스의 개념

데이터패스(Data Path)란 CPU 내부에서 데이터가 이동하는 경로를 의미하며,

명령어 실행 과정에서 연산 수행, 데이터 이동, 저장 등의 역할을 담당합니다.

💡 쉽게 말해:

- CPU가 명령어를 실행할 때, 데이터가 이동하는 경로

- ALU(연산 장치), 레지스터, 버스 등이 데이터를 전달하는 핵심 요소

- CPU 성능을 결정하는 중요한 구조 중 하나

✅ 데이터패스는 CPU의 기본 연산을 처리하는 핵심 요소

🔹 2. 데이터패스의 주요 구성 요소

데이터패스는 다음과 같은 주요 하드웨어 구성 요소로 이루어져 있습니다.

| 구성 요소 | 설명 |

| 연산 장치(ALU, Arithmetic Logic Unit) | 산술 및 논리 연산 수행 |

| 레지스터(Register) | 데이터를 저장하고 연산 결과를 보관 |

| 멀티플렉서(Multiplexer, MUX) | 여러 입력 신호 중 하나를 선택하여 전송 |

| 버스(Bus) | CPU 내부에서 데이터가 이동하는 통로 |

| 제어 신호(Control Signals) | 데이터 이동 및 연산을 제어 |

💡 데이터패스는 명령어 실행을 위해 데이터를 처리하고 이동시키는 구조

🔹 3. 데이터패스의 동작 과정

데이터패스는 CPU의 명령어 실행 과정(Fetch → Decode → Execute → Write Back) 에 따라 데이터를 전달합니다.

✅ 3.1 데이터 흐름의 기본 과정

1️⃣ 명령어 가져오기(Fetch)

- 메모리에서 명령어를 읽어와 명령어 레지스터(IR)에 저장

- 프로그램 카운터(PC)가 다음 명령어의 주소를 갱신

2️⃣ 명령어 해석(Decode)

- 명령어를 분석하여 필요한 연산과 데이터 경로를 설정

- 레지스터에서 데이터를 가져와 ALU로 전달

3️⃣ 연산 수행(Execute)

- ALU가 연산을 수행하여 결과를 생성

- 데이터가 메모리로 저장되거나 레지스터에 저장됨

4️⃣ 결과 저장(Write Back)

- 연산 결과를 레지스터 또는 메모리에 기록하여 다음 연산을 준비

💡 데이터패스는 CPU 내부에서 데이터를 올바르게 전달하고 처리하는 핵심 구조!

✅ 3.2 데이터패스의 예제 (ADD 연산)

💡 예제: R1 = R2 + R3 (MIPS 명령어: ADD R1, R2, R3)

- 명령어 가져오기 (Fetch) → 명령어를 메모리에서 가져와 IR에 저장

- 명령어 해석 (Decode) → R2와 R3의 값을 레지스터에서 읽음

- 연산 수행 (Execute) → ALU에서 R2 + R3 연산 수행

- 결과 저장 (Write Back) → 연산 결과를 R1 레지스터에 저장

💡 이 과정에서 데이터가 ALU, 레지스터, 버스를 통해 이동함!

🔹 4. 데이터패스의 유형

데이터패스의 구현 방식은 싱글사이클(Single Cycle), 멀티사이클(Multi Cycle), 파이프라인(Pipelined) 방식으로 나뉩니다.

| 데이터패스 유형 | 설명 | 장점 | 단점 |

| 싱글사이클(Single Cycle) | 하나의 명령어를 한 사이클에서 처리 | 구조가 단순함 | 성능이 낮음 |

| 멀티사이클(Multi Cycle) | 명령어를 여러 사이클에 걸쳐 실행 | 성능이 향상됨 | 제어가 복잡함 |

| 파이프라인(Pipelined) | 여러 명령어를 동시에 실행 | 처리 속도가 빠름 | 데이터 충돌 발생 가능 |

💡 현대 CPU는 대부분 "파이프라인 방식"을 사용하여 성능을 최적화함

🔹 5. 데이터패스 최적화 기법

현대 CPU는 성능을 향상시키기 위해 데이터패스를 최적화하는 다양한 기법을 적용합니다.

✅ 파이프라이닝(Pipelining) → 명령어를 여러 단계로 나누어 동시에 실행

✅ 슈퍼스칼라(Superscalar) → 한 사이클에 여러 명령어 실행

✅ 레지스터 리네이밍(Register Renaming) → 데이터 충돌 방지

✅ 브랜치 예측(Branch Prediction) → 분기 명령어의 실행 지연 최소화

💡 데이터패스 최적화는 CPU의 속도를 극대화하는 핵심 기술!

🔹 6. 데이터패스의 실제 적용 사례

현대 CPU 아키텍처는 고성능 데이터패스를 적용하여 연산 속도를 최적화하고 있습니다.

| CPU 아키텍처 | 데이터패스 특징 |

| MIPS | 단순한 RISC 데이터패스 (파이프라인 최적화) |

| x86 (Intel, AMD) | 복잡한 CISC 데이터패스 (슈퍼스칼라, 아웃오브오더 실행) |

| ARM | 저전력 최적화된 데이터패스 (모바일 최적화) |

💡 x86 CPU는 복잡한 데이터패스를 사용하여 고성능을 추구

💡 ARM CPU는 전력 효율성을 위해 최적화된 데이터 흐름을 적용

✅ 마무리: 데이터패스의 핵심 정리

✅ 데이터패스는 CPU 내부에서 데이터가 이동하는 경로

✅ ALU, 레지스터, 버스, 멀티플렉서 등으로 구성됨

✅ 명령어 실행 과정(Fetch → Decode → Execute → Write Back)에서 데이터 흐름을 담당

✅ 파이프라이닝, 슈퍼스칼라, 브랜치 예측 등의 기법으로 최적화 가능

'IT > 컴퓨터구조' 카테고리의 다른 글

| 🖥️ [컴퓨터구조] 파이프라이닝(Pipelining)의 개념 (0) | 2025.03.11 |

|---|---|

| 🖥️ [컴퓨터구조] CPU의 명령어 실행 과정 (IF, ID, EX, MEM, WB) (0) | 2025.03.10 |

| 🖥️ [컴퓨터구조] CPU 내부 구조 개요 (0) | 2025.03.08 |

| 🖥️ [컴퓨터구조] 연산 속도를 높이는 방법 (병렬 연산, SIMD, 벡터 연산) (1) | 2025.03.07 |

| 🖥️ [컴퓨터구조] 부동소수점 연산 (IEEE 754 표준) (0) | 2025.03.06 |